По какой шине передаются лишь выходные сигналы микропроцессора

УСТРОЙСТВ. РЕЖИМЫ ФУНКЦИОНИРОВАНИЯ

СТРУКТУРА МИКРОПРОЦЕССОРНЫХ

УСТРОЙСТВ. РЕЖИМЫ ФУНКЦИОНИРОВАНИЯ

Применение МП позволило создать новый класс вычислительной техники — микропроцессорные системы, обобщенная логическая структура которых приведена на рисунке 1.

Центральное место в этой структуре занимает микропроцессор, который выполняет арифметические и логические операции над данными, осуществляет программное управление процессом обработки информации, организует взаимодействие всех устройств, входящих в систему. Работа МП происходит под воздействием сигналов схемы синхронизации и начальной установки, часто выполняемой в виде отдельного кристалла.

Показанный на рисунке 1 МП может представлять собой или однокристальный МП с фиксированной системой команд или многокристальный МП с микропрограммным управлением.

Представленная на рисунке 1 структура отражает магистрально-модульный принцип организации микропроцессорных устройств и систем. Отдельные блоки являются функционально законченными модулями со своими встроенными схемами управления, выполненными в виде одного или нескольких кристаллов БИС или СБИС. Межмодульные связи и обмен информацией между модулями осуществляются посредством коллективных шин (магистралей), к которым имеют доступ все основные модули системы. В каждый данный момент времени возможен обмен информацией только между двумя модулями системы.

Магистральный принцип построения сопряжения модулей (интерфейс ЭВМ) предполагает наличие информационно-логической совместимости модулей, которая реализуется путем использования единых способов представления информации, алгоритма управления обменом, форматов команд и способа синхронизации.

Для большинства микропроцессоров характерна трехшинная структура, содержащая шину адреса (ША), двунаправленную шину данных (ШД) и шину управления (ШУ). Как видно из рисунка 1, типовая структура МП-системы предполагает наличие общего сопряжения для модулей памяти (постоянных и оперативных запоминающих устройств) и периферийных устройств (устройств ввода-вывода).

В качестве периферийных устройств в МП-системах используются устройства ввода с перфоленты, дисплеи, магнитофоны, гибкие и жесткие магнитные диски, телетайпы, печатающие устройства, клавиатура и т.п.

Периферийное устройство подсоединяется к шинам МП не непосредственно, а через программируемый периферийный адаптер (ППА) или программируемый связной адаптер (ПСА), обслуживающие периферийные устройства соответственно с передачей информации параллельным или последовательным кодом. Наличие программно настраиваемых адаптеров делает весьма гибкой и функционально богатой систему ввода-вывода информации в МП-системе.

Постоянное запоминающее устройство (ПЗУ) хранит системные программы, необходимые для управления процессом обработки. В оперативном запоминающем устройстве (ОЗУ) хранятся прикладные программы, данные и результаты вычислений.

Работа МП синхронизируется тактовыми сигналами CLK, поступающими на его входы от генератора синхронизации. Схема начальной установки вырабатывает сигнал RESET (сброса) микропроцессора на основе анализа напряжений на выходе блока питания или при принудительной остановке работы МПС с ее клавиатуры.

В состав этих МПС, как правило, входят:

— шинный контролер для сопряжения устройств с системной шиной по параллельному интерфейсу;

— адаптер последовательного интерфейса для построения многопроцессорных систем или сопряжения источников и приемников сигналов, не увеличивающих нагрузку на системный интерфейс;

— специализированный процессор арифметической обработки сигналов (сопроцессор);

— ПЗУ команд и констант;

Для обеспечения работы МПС к их системному интерфейсу можно подключать устройства специализированной обработки арифметических алгоритмов, таких как быстрое преобразование Фурье, и устройства обработки аналоговых сигналов.

В состав таких устройств обработки аналоговых сигналов входят:

-аналого-цифровые (АЦП) и цифроаналоговые (ЦАП) преобразователи, обеспечивающие непосредственное сопряжение цифрового устройства обработки с аналоговыми сигналами датчиков и приемников;

— система памяти ПЗУ и ОЗУ;

— буферы данных, используемые для временного хранения (буферизации) данных при передаче между устройствами;

— МП, предназначенный для цифровой обработки аналоговых сигналов.

В рассматриваемых структурах МПС реализуются три способа организации (обслуживания) передачи информации:

1) программно-управляемая передача, инициируемая процессором;

2) программно-управляющая передача, инициируемая запросом прерывания от периферийного устройства;

3) прямой доступ к памяти (ПДП).

При первом способе передача инициируется самим процессором, а при втором — запросом прерывания от периферийного устройства.

При программно-управляемой передаче данных МП на все время этой операции отвлекается от выполнения основной программы, что ведет к снижению производительности МП-системы. Кроме того, скорость передачи данных через МП может оказаться недостаточной для работы с высокоскоростными внешними устройствами.

Прямым доступом к памяти называется способ обмена данными, обеспечиваюший автономно от МП установление связи и передачу данных между ОЗУ и внешним устройством.

Прямой доступ к памяти, повышая предельную скорость ввода-вывода информации и общую производительность МП-системы, делает ее более приспособленной для работы в системах реального времени. Прямым доступом к памяти управляет контролер ПДП, выполяющий следующие функции:

— управление инициируемой процессором или ПУ передачей данных между ОЗУ и ПУ;

— задание размера блока данных, который подлежит передаче, и области памяти, используемой при передаче;

— формирование адресов ячеек ОЗУ, участвующих в передаче;

— подсчет числа байт, передаваемых через интерфейс, и определение момента завершения заданной операции ввода-вывода.

3 Шиной системы называют физическую группу линий передачи сигналов, имеющих схожие функции в рамках системы. Все три шины являются специализированными с точки зрения их функций. Эти шины именуются так:

а) адресная шина;

в) шина управления.

По адресной шине передаются лишь выходные сигналы микропроцессора, т. е. от микропроцессора к внешнему устройству. Эта шина предназначена для того, чтобы открывать или выбирать правильный тракт для электрического соединения в пределах микропроцессорной системы.

Для удобства будем в дальнейшем полагать, что все электрические соединения в микропроцессорной системе осуществляются между микропроцессором и устройством, открытым (выбранным) с помощью адресной шины. В качестве устройства здесь выступает любая электрическая схема, принимающая данные от микропроцессора либо вырабатывающая данные для него.

Важнейшей характеристикой адресной шины является ее емкость. Емкость шины определяется числом входящих в нее отдельных электрических линий. К примеру, 16-разрядная адресная шина представляет собой 16 независимых физических линий для передачи электрических сигналов.

Шина данных является двунаправленной шиной. Это означает, что передача данных может производиться в обоих направлениях. В первом случае, данные передаются от микропроцессора во внешнее устройство (выбранное адресной шиной ). Этот режим называется выводом данных. Во втором случае, данные передаются от внешнего устройства (выбранного шиной адреса) в микропроцессор. Этот режим называется вводом данных.

Хотя передача данных по шине данных может производиться в обоих направлениях, однако в каждый заданный момент времени она осуществляется лишь в одном из двух направлений. Это означает, что для передачи данных в устройство (систему) и их приема из системы микропроцессор переводится в соответствующий режим. Также как и адресная шина, шина данных обладает определенной емкостью (разрядностью). По емкости шины данных судят о классе микропроцессора. К примеру, при 8-разрядной шине данных микропроцессор будет отнесен к классу 8-разрядных микропроцессоров.

На шине управления действует несколько типов сигналов. Основные из них:

а) чтение данных из памяти;

б) запись данных в память;

в) чтение данных с устройства ввода-вывода;

г) запись данных в устройство ввода-вывода.

Позднее для этой шины мы введем некоторые добавочные сигналы. Однако для понимания существа процессов пока достаточно ограничиться указанным списком сигналов. Шина управления используется лишь для вывода сигналов, т. е. является однонаправленной.

Источник: lektsii.org

Архитектура микропроцессора

Архитектура с тремя шинами является наиболее общей для микропроцессорных систем. Шиной системы называют физическую группу линий передачи сигналов, имеющих схожие функции в рамках системы. Все три шины являются специализированными с точки зрения их функций. Эти шины именуются так:

а) адресная шина;

в) шина управления.

По адресной шине передаются лишь выходные сигналы микропроцессора, т. е. от микропроцессора к внешнему устройству. Эта шина предназначена для того, чтобы открывать или выбирать правильный тракт для электрического соединения в пределах микропроцессорной системы.

Для удобства будем в дальнейшем полагать, что все электрические соединения в микропроцессорной системе осуществляются между микропроцессором и устройством, открытым (выбранным) с помощью адресной шины. В качестве устройства здесь выступает любая электрическая схема, принимающая данные от микропроцессора либо вырабатывающая данные для него.

Важнейшей характеристикой адресной шины является ее емкость. Емкость шины определяется числом входящих в нее отдельных электрических линий. К примеру, 16-разрядная адресная шина представляет собой 16 независимых физических линий для передачи электрических сигналов.

Шина данных является двунаправленной шиной. Это означает, что передача данных может производиться в обоих направлениях. В первом случае, данные передаются от микропроцессора во внешнее устройство (выбранное адресной шиной ). Этот режим называется выводом данных. Во втором случае, данные передаются от внешнего устройства (выбранного шиной адреса) в микропроцессор. Этот режим называется вводом данных.

Хотя передача данных по шине данных может производиться в обоих направлениях, однако в каждый заданный момент времени она осуществляется лишь в одном из двух направлений. Это означает, что для передачи данных в устройство (систему) и их приема из системы микропроцессор переводится в соответствующий режим. Также как и адресная шина, шина данных обладает определенной емкостью (разрядностью). По емкости шины данных судят о классе микропроцессора. К примеру, при 8-разрядной шине данных микропроцессор будет отнесен к классу 8-разрядных микропроцессоров.

На шине управления действует несколько типов сигналов. Основные из них:

а) чтение данных из памяти;

б) запись данных в память;

в) чтение данных с устройства ввода-вывода;

г) запись данных в устройство ввода-вывода.

Позднее для этой шины мы введем некоторые добавочные сигналы. Однако для понимания существа процессов пока достаточно ограничиться указанным списком сигналов. Шина управления используется лишь для вывода сигналов, т. е. является однонаправленной.

НОВОСТИ ФОРУМА Рыцари теории эфира |

01.10.2019 — 05:20: ВОСПИТАНИЕ, ПРОСВЕЩЕНИЕ, ОБРАЗОВАНИЕ — Upbringing, Inlightening, Education -> [center][Youtube]69vJGqDENq4[/Youtube][/center][center]14:36[/center]Osievskii Global News 29 сент. Отправлено 05:20, 01.10.2019 г.’ target=_top>Просвещение от Вячеслава Осиевского — Карим_Хайдаров. 30.09.2019 — 12:51: ВОСПИТАНИЕ, ПРОСВЕЩЕНИЕ, ОБРАЗОВАНИЕ — Upbringing, Inlightening, Education -> [center][Ok]376309070[/Ok][/center][center]11:03[/center] Отправлено 12:51, 30.09.2019 г.’ target=_top>Просвещение от Дэйвида Дюка — Карим_Хайдаров. 30.09.2019 — 11:53: ВОСПИТАНИЕ, ПРОСВЕЩЕНИЕ, ОБРАЗОВАНИЕ — Upbringing, Inlightening, Education -> [center][Youtube]VVQv1EzDTtY[/Youtube][/center][center]10:43[/center] |

интервью Раввина Борода https://cursorinfo.co.il/all-news/rav.

мой телеграмм https://t.me/peshekhonovandrei

мой твиттер https://twitter.com/Andrey54708595

мой инстаграм https://www.instagram.com/andreipeshekhonow/

Андрей спрашивает: Краснодарская синагога — это что, военный объект?

— Да, военный, потому что имеет разрешение от Росатома на манипуляции с радиоактивными веществами, а также иными веществами, опасными в отношении массового поражения. Именно это было выявлено группой краснодарцев во главе с Мариной Мелиховой. [center][Youtube]CLegyQkMkyw[/Youtube][/center]

[center]10:22 [/center]

Доминико Риккарди: Россию ждёт страшное будущее (хотелки ЦРУ):

https://tainy.net/22686-predskazaniya-dominika-rikardi-o-budushhem-rossii-sdelannye-v-2000-godu.html

Завещание Алена Даллеса / Разработка ЦРУ (запрещено к ознакомлению Роскомнадзором = Жид-над-рус-надзором)

http://av-inf.blogspot.com/2013/12/dalles.html

[center]10:22 [/center]

Доминико Риккарди: Россию ждёт страшное будущее (хотелки ЦРУ):

https://tainy.net/22686-predskazaniya-dominika-rikardi-o-budushhem-rossii-sdelannye-v-2000-godu.html

Завещание Алена Даллеса / Разработка ЦРУ (запрещено к ознакомлению Роскомнадзором = Жид-над-рус-надзором)

http://av-inf.blogspot.com/2013/12/dalles.html

Источник: bourabai.kz

Управляющие сигналы типового микропроцессора

Кроме информационных линий адреса и данных, микропроцессор снабжен управляющими выводами, образующими вместе с выводами системного контроллера шину управления микропроцессорной системы. Управлюющие сигналы индивидуальны для каждого типа микропроцессора, но, тем не менее, можно выделить характерные для почти всех микропроцессоров сигналы. В некоторых случаях определенные сигналы исключают друг друга, поэтому присутствуют либо те, либо другие. Разобъем управляющие сигналы для удобства в функциональные группы.

Сигналы управления чтением/записью предназначены для активизации периферийного модуля в режим выдачи данных на шину данных или приема данных с шины данных. В общем случае режим чтения характеризуется тем, что микропроцессор запрашивает данные от периферийного модуля, а режим записи — тем, что микропроцессор выставляет данные периферийному модулю. У некоторых микропроцессоров эти сигналы представлены группой сигналов системной шины управления, рассмотренных ранее в теме структурной организации микропроцессорной системы:

· RDM (read memory, чтение памяти) — сигнал инициализации чтения из модулей запоминающих устройств (выходной сигнал);

· WRM (write memory, запись в память) — сигнал инициализации записи в модули запоминающих устройств (выходной сигнал);

· RDIO (read input/output, чтение порта) — сигнал инициализации чтения из порта ввода (выходной сигнал);

· WRIO (write input/output, запись в порт) — сигнал инициализации записи в порт вывода (выходной сигнал).

Есть микропроцессоры, в которых сигналы управления чтением/записью образуются сигналами, указывающими направление передачи информации и тип адресуемого модуля:

· RD (read, чтение) – сигнал инициализации чтения из периферийного модуля (выходной сигнал);

· WR (write, запись) – сигнал инициализации записи в периферийный модуль (выходной сигнал);

· MEM (memory, память) – сигнал обращения к памяти (выходной сигнал);

· I/O (input/output, порты ввода-вывода) – сигнал обращения к портам ввода-вывода (выходной сигнал).

Режимы обращения к памяти или к портам исключают друг друга в одном машинном цикле. Поэтому часто вместо пары сигналов MEM и I/O на выводах микропроцессора присутствует только один сигнал  . Единичный уровень этого сигнала соответствует режиму обращения к памяти, а нулевой – режиму обращения к портам ввода-вывода. Для формирования сигналов RDM, WRM, RDIO и WRIO системной шины управления, если таких нет на выводах микропроцессора, из сигналов RD, WR, MEM и I/O микропроцессора можно спроектировать схему на основе вентилей элементарных логических функций или воспользоваться системным контроллером.

. Единичный уровень этого сигнала соответствует режиму обращения к памяти, а нулевой – режиму обращения к портам ввода-вывода. Для формирования сигналов RDM, WRM, RDIO и WRIO системной шины управления, если таких нет на выводах микропроцессора, из сигналов RD, WR, MEM и I/O микропроцессора можно спроектировать схему на основе вентилей элементарных логических функций или воспользоваться системным контроллером.

Сигналы управления прерыванием обычно представлены двумя сигналами:

· INT (interrupt, прерывание) – входной сигнал от периферийного модуля (контроллера прерывания), запрашивающего процесс ввода-вывода по прерыванию. В ответ на этот сигнал микропроцессор должен запустить обрабатывающую прерывание подпрограмму. Анализируется этот сигнал в последнем такте последнего машинного цикла, т.е. в конце выполнения текущей команды;

· INTA (interrupt acknowledge, подтверждение прерывания) – выходной сигнал от микропроцессора, подтверждающий прерывание и сообщающий периферийному модулю (контроллеру прерывания) о готовности микропроцессора приступить к обслуживанию прерывания. По этому сигналу внешнее устройство (контроллер прерывания) должен выставить на шину данных код команды прерывания, в которой закодирован номер устройства, запрашивающего прерывание.

Сигналы управления режимом прямого доступа к памяти формируют группу из двух сигналов:

· HOLD (hold, захват шин) – входной сигнал от периферийного устройства, запрашивающего процесс ввода-вывода в режиме ПДП. Этот сигнал анализируется обычно между машинными циклами. В ответ на этот сигнал микропроцессор должен перевести свои буферные регистры, связывающие его с шинами данных и адреса, в высокоимпедансное состояние. В результате микропроцессор осовобождает шины и внешнее устройство начинает обмен данными с памятью напрямую без участия микропроцессора;

· HLDA (hold acknowledge, подтверждение захвата) – выходной сигнал от микропроцессора, подтверждающий, что микропроцессор перевел свои буферные регистры в высокоимпедансное состояние и освободил шины.

Сигналы управления ожиданием служат для синхронизации микропроцессора с медленными устройствами ввода-вывода. Не всегда внешнее устройство может мгновенно отреагировать и подготовиться к режиму приема или записи по сигналам RDIO или WRIO (RD или WR). Если внешнее устройство медленное, то ему необходимо время для формирования данных или включения в соответствующий режим. Для синхронизации работы микропроцессора с медленными устройствами ввода-вывода используются следующие сигналы:

· RDY (ready, готовность) – входной сигнал от внешнего устройства, являющийся признаком того, что оно готово к обмену данными. Если этот сигнал имеет пассивный уровень, то микропроцессор переходит в такты ожидания готовности внешнего утройства. В течение этого времени микропроцессор не выполняет никаких действий, а только анализирует сигнал готовности;

· WAIT (wait, ожидание) – выходной сигнал, являющийся признаком того, что микропроцессор находится в тактах ожидания сигнала готовности.

Дополнительные сигналы обеспечивают синхронизацию работы микропроцессора с системным контроллером, шинными формирователями, схемой тактового генератора и начальной установки. К ним можно отнести следующие сигналы:

· SYNC (synchronization, синхронизация) – выходной сигнал, вырабатываемый микропроцессором в начале каждого машинного цикла. Он служит для записи в системный контроллер служебной информации, из которой системный контроллер формирует дополнительные сигналы управления (например, RDM, WRM, RDIO и WRIO);

· ALE (address latch enable, фиксация адреса) – выходной сигнал микропроцессора, имеющего мультиплексированную шину данных/адреса. Мультиплесированная шина позволяет уменьшить количество выводов микросхемы микропроцессора, поскольку разряды шины данных и адреса реализуются в таких микропроцессорах на одних и тех же выводах. В начале машинного цикла всегда должен быть выставлен адрес внешнего устройства или ячейки памяти, а лишь затем произведен обмен информацией. Поэтому шину данных и адреса можно объединить в одну мультиплексированную шину. Но адрес должен удерживаться на время всего машинного цикла. Для этого сигналом ALE, который выставляется активным вместе с выставлением адреса на мультиплексированной шине, адрес записывается во внешний регистр (шинный формирователь) и там защелкивается до следующего машинного цикла. Затем мультиплексированная шина переключается в режим шины данных;

· RST (reset, сброс) – входной сигнал сброса, обнуляющий регистр микропроцессора, содержащий адреса подлежащих выполнению команд и называемый счетчиком команд. В результате программа начинает выполняться с нулевого адреса, т.е. с начала;

· CLK (clock, тактирование) – вход (входы) сигналов тактового генератора. Эти сигналы синхронизируют работу микропроцессора. По этим сигналам часто оценивают производительность микропроцессора.

Дата добавления: 2014-01-06 ; Просмотров: 3424 ; Нарушение авторских прав?

Нам важно ваше мнение! Был ли полезен опубликованный материал? Да | Нет

Источник: studopedia.su

Шины микропроцессорной системы

Шина данных — это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд.

Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями.

Обычно шина данных имеет 8, 16, 32 или 64 разряда. Разрядность шины данных определяет и разрядность всей магистрали.

Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Например, 16-разрядная шина адреса обеспечивает 65 536 адресов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП). Наиболее часто используются типы выходных каскадов с тремя состояниями или обычные ТТЛ (с двумя состояниями).

Как в шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий — логическому нулю. При отрицательной логике — наоборот. В большинстве случаев уровни сигналов на шинах — ТТЛ.

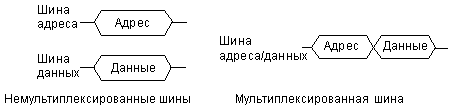

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (рис. 2.1). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

Рис.2. 1. Мультиплексирование шин адреса и данных.

В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям.

Шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

Сигналы шины управления могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще). Линии шины управления могут быть как однонаправленными, так и двунаправленными. Типы выходных каскадов могут быть самыми разными: с двумя состояниями (для однонаправленных линий), с тремя состояниями (для двунаправленных линий), с открытым коллектором (для двунаправленных и мультиплексированных линий).

Самые главные управляющие сигналы — это стробы обмена, то есть сигналы, формируемые процессором и определяющие моменты времени, в которые производится пересылка данных по шине данных, обмен данными. Чаще всего в магистрали используются два различных строба обмена:

Строб записи (вывода), который определяет момент времени, когда устройство-исполнитель может принимать данные, выставленные процессором на шину данных;

Строб чтения (ввода), который определяет момент времени, когда устройство-исполнитель должно выдать на шину данных код данных, который будет прочитан процессором.

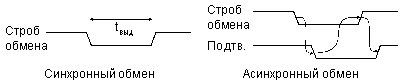

При этом большое значение имеет то, как процессор заканчивает обмен в пределах цикла, в какой момент он снимает свой строб обмена. Возможны два пути решения (рис. 2.2):

При синхронном обмене процессор заканчивает обмен данными самостоятельно, через раз и навсегда установленный временной интервал выдержки (tвыд), то есть без учета интересов устройства-исполнителя;

При асинхронном обмене процессор заканчивает обмен только тогда, когда устройство-исполнитель подтверждает выполнение операции специальным сигналом (так называемый режим handshake — рукопожатие).

Рис. 2.2. Синхронный обмен и асинхронный обмен.

Достоинства синхронного обмена — более простой протокол обмена, меньшее количество управляющих сигналов. Недостатки — отсутствие гарантии, что исполнитель выполнил требуемую операцию, а также высокие требования к быстродействию исполнителя.

Достоинства асинхронного обмена — более надежная пересылка данных, возможность работы с самыми разными по быстродействию исполнителями. Недостаток — необходимость формирования сигнала подтверждения всеми исполнителями, то есть дополнительные аппаратурные затраты.

По используемому типу обмена магистрали микропроцессорных систем также делятся на синхронные и асинхронные.

Не нашли то, что искали? Воспользуйтесь поиском:

Лучшие изречения: Для студентов недели бывают четные, нечетные и зачетные. 9958 —  | 7746 —

| 7746 —  или читать все.

или читать все.

Источник: studopedia.ru

Микропроцессоры и микро-ЭВМ

Главная > Конспект >Информатика, программирование

Постоянное запоминающее устройство (ПЗУ) хранит системные программы, необходимые для управления процессом обработки. В оперативном запоминающем устройстве (ОЗУ) хранятся прикладные программы, данные и результаты вычислений.

Работа МП синхронизируется тактовыми сигналами CLK, поступающими на его входы от генератора синхронизации. Схема начальной установки вырабатывает сигнал RESET (сброса) микропроцессора на основе анализа напряжений на выходе блока питания или при принудительной остановке работы МПС с ее клавиатуры.

В состав этих МПС, как правило, входят:

— шинный контролер для сопряжения устройств с системной шиной по параллельному интерфейсу;

— адаптер последовательного интерфейса для построения многопроцессорных систем или сопряжения источников и приемников сигналов, не увеличивающих нагрузку на системный интерфейс;

— специализированный процессор арифметической обработки сигналов (сопроцессор);

— ПЗУ команд и констант;

Для обеспечения работы МПС к их системному интерфейсу можно подключать устройства специализированной обработки арифметических алгоритмов, таких как быстрое преобразование Фурье, и устройства обработки аналоговых сигналов.

В состав таких устройств обработки аналоговых сигналов входят:

-аналого-цифровые (АЦП) и цифроаналоговые (ЦАП) преобразователи, обеспечивающие непосредственное сопряжение цифрового устройства обработки с аналоговыми сигналами датчиков и приемников;

— система памяти ПЗУ и ОЗУ;

— буферы данных, используемые для временного хранения (буферизации) данных при передаче между устройствами;

— МП, предназначенный для цифровой обработки аналоговых сигналов.

В рассматриваемых структурах МПС реализуются три способа организации (обслуживания) передачи информации:

1) программно-управляемая передача, инициируемая процессором;

2) программно-управляющая передача, инициируемая запросом прерывания от периферийного устройства;

3) прямой доступ к памяти (ПДП).

При первом способе передача инициируется самим процессором, а при втором — запросом прерывания от периферийного устройства.

При программно-управляемой передаче данных МП на все время этой операции отвлекается от выполнения основной программы, что ведет к снижению производительности МП-системы. Кроме того, скорость передачи данных через МП может оказаться недостаточной для работы с высокоскоростными внешними устройствами.

Прямым доступом к памяти называется способ обмена данными, обеспечиваюший автономно от МП установление связи и передачу данных между ОЗУ и внешним устройством.

Прямой доступ к памяти, повышая предельную скорость ввода-вывода информации и общую производительность МП-системы, делает ее более приспособленной для работы в системах реального времени. Прямым доступом к памяти управляет контролер ПДП, выполяющий следующие функции:

— управление инициируемой процессором или ПУ передачей данных между ОЗУ и ПУ;

— задание размера блока данных, который подлежит передаче, и области памяти, используемой при передаче;

— формирование адресов ячеек ОЗУ, участвующих в передаче;

— подсчет числа байт, передаваемых через интерфейс, и определение момента завершения заданной операции ввода-вывода.

2.1 Архитектура с тремя шинами

Архитектура с тремя шинами является наиболее общей для микропроцессорных систем. Шиной системы называют физическую группу линий передачи сигналов, имеющих схожие функции в рамках системы. Все три шины являются специализированными с точки зрения их функций. Эти шины именуются так:

а) адресная шина;

в) шина управления.

По адресной шине передаются лишь выходные сигналы микропроцессора, т. е. от микропроцессора к внешнему устройству. Эта шина предназначена для того, чтобы открывать или выбирать правильный тракт для электрического соединения в пределах микропроцессорной системы.

Для удобства будем в дальнейшем полагать, что все электрические соединения в микропроцессорной системе осуществляются между микропроцессором и устройством, открытым (выбранным) с помощью адресной шины. В качестве устройства здесь выступает любая электрическая схема, принимающая данные от микропроцессора либо вырабатывающая данные для него.

Важнейшей характеристикой адресной шины является ее емкость. Емкость шины определяется числом входящих в нее отдельных электрических линий. К примеру, 16-разрядная адресная шина представляет собой 16 независимых физических линий для передачи электрических сигналов.

Шина данных является двунаправленной шиной. Это означает, что передача данных может производиться в обоих направлениях. В первом случае, данные передаются от микропроцессора во внешнее устройство (выбранное адресной шиной ). Этот режим называется выводом данных. Во втором случае, данные передаются от внешнего устройства (выбранного шиной адреса) в микропроцессор. Этот режим называется вводом данных.

Хотя передача данных по шине данных может производиться в обоих направлениях, однако в каждый заданный момент времени она осуществляется лишь в одном из двух направлений. Это означает, что для передачи данных в устройство (систему) и их приема из системы микропроцессор переводится в соответствующий режим. Также как и адресная шина, шина данных обладает определенной емкостью (разрядностью). По емкости шины данных судят о классе микропроцессора. К примеру, при 8-разрядной шине данных микропроцессор будет отнесен к классу 8-разрядных микропроцессоров.

На шине управления действует несколько типов сигналов. Основные из них:

а) чтение данных из памяти;

б) запись данных в память;

в) чтение данных с устройства ввода-вывода;

г) запись данных в устройство ввода-вывода.

Позднее для этой шины мы введем некоторые добавочные сигналы. Однако для понимания существа процессов пока достаточно ограничиться указанным списком сигналов. Шина управления используется лишь для вывода сигналов, т. е. является однонаправленной.

3 Архитектура 8-разрядного однокристального

микропроцессора серии К580

3.1 Общая характеристика однокристального МП

Микропроцессор КР580ИК80А является программируемой универсальной БИС, может считывать информацию из внешних устройств, памяти и производить над ней арифметические и логические операции, анализировать результаты вычислений и записывать данные в память и внешние устройства, функционируя при этом под управлением команд из некоторого фиксированного множества.

Микропроцессорная БИС КР580ИК80 представляет собой однокристальный 8-разрядный МП с двумя магистралями: однонаправленной 16-разрядной адресной магистралью (МА), двунаправленной 8-разрядной магистралью данных (МД) и 12 сигналами управления (шесть входных и шесть выходных).

Таблица 1 — Технические характеристики БИС КР580ИК80

Условное обозначение МП БИС К580ИК80 приведено на рисунке 2.

Функциональное назначение внешних

выводов МП БИС КР580ИК80:

Адресная шина (А0-А15) , обеспечи-

вающая адресацию к любой из 216

8-разрядной ячейке памяти или внеш-

него устройства (ВУ);

Двунаправленная шина данных

(Д0-Д7), используемая для обмена

информации с памятью или ВУ;

Шина управления (выходная) :

СИНХР (SYNC) — на этом выходе МП

БИС фпрмируется сигнал СИНХР в

начале каждого машинного цикла;

П (DBIN,прием) — сигнал ПРИЕМ

на этом выходе указывает на готов-

ность МП БИС к приему данных;

ОЖД (WAIT,ожидание) — сигнал ОЖД

на этом выходе указывает что МП

находится в состоянии ожидания;

ЗП (WR)- на этом выходе МП БИС

сигнал ЗП указывает, что данные

выданы МП БИС и установлены на

МД (магистраль данных) и могут быть

П.ЗХ (HLDA, подтверждение захвата) — на этом выходе МП БИС сигнал П.ЗХ появляется в ответ на сигнал З.ЗХ (запрос захвата) и указывает, что МД и МА находятся в состоянии высокого сопротивления;

Р.ПР (INTE, разрешение прерывания) — на этом выходе сигнал Р.ПР указывает на состояние внутреннего триггера разрешения прерывания МП БИС. Состояние триггера может быть установлено программно с помощью команд EI,DI. При уровне “0” на выходе Р.ПР прием запросов прерывания МП БИС невозможен.

Шина управления (входная):

Г (READY, готов) — сигнал ГОТОВ на этом входе информирует о готовности ВУ к обмену информацией с МП БИС . При уровне “0” МП БИС будет находиться в состоянии ОЖИДАНИЕ.

З.ЗХ (HOLT, запрос захвата) — вход, используемый для подачи сигнала З.ЗХ на переход МП БИС в состояние ЗАХВАТ, в котором МА и МД переходят в третье состояние (высокое сопротивление). Обычно состояние используется для организации обмена информацией по каналу прямого доступа к памяти;

З.ПР (INT, запрос прерывания) — вход, используемый для подачи сигнала З.ПР. Сигнал поступает от внешнего источника на прерывание выполнения основной программы и переход на выполнение подпрограмм обслуживания прерывания. Сигнал запроса прерывания не воспринимается МП БИС при работе его в режимах ЗАХВАТ, ОЖИДАНИЕ или нулевом состоянии внутреннего тригера разрешения прерывания;

R (RESET)- вход, по которому поступает сигнал на начальную установку МП БИС, при этом обнуляется его программный счетчик, внутренние триггеры, формирующие сигналы Р.ПР и П.ЗХ;

CLK1,2 — входы для подачи тактовых сигналов Ф1(СДК1) и Ф2(СДК2). Эти сигналы являются не пересекающимися во времени сигналами, определяющими тактовую частоту работы МП БИС.

Источник: works.doklad.ru