По какой шине передается адрес порта

Шина данных. разрядность шины

Шину данных образуют линии, служащие для передачи данных между отдельными структурными группами ПК. Исходным пунктом линий данных является центральный процессор. Он определяет разрядность шины данных, т.е. число линий, по которым передаются данные. Чем выше разрядность шины данных, тем больший объем данных можно передать по ней за некоторый определенный промежуток времени и тем выше быстродействие компьютера.

В первых ПК использовался процессор Intel 8088. Этот 16-разрядный процессор имел всего лишь 8 внешних линий данных (этим объясняется его низкая стоимость). Для внутренних операций было задействовано 16 линий данных, благодаря чему процессор мог одновременно обрабатывать два восьмиразрядных числа. Но на внешнем уровне к нему присоединялась дешевая восьмиразрядная шина данных. Эти 8 линий обеспечивали связь со всеми микросхемами на системной плате, выполняющими функции обработки данных, и всеми платами расширения, установленными в гнездах. Таким образом осуществлялась передача данных между платами расширения и процессором.

Современные процессоры допускают внешнее подключение большего числа линий данных: процессор 80286 — 16 линий данных, процессоры 80386 DX и 80486 DX — 32 линии, а процессор Pentium — 64 линии данных.

Адресная шина. Разрядность шины

Другая группа линий образует адресную шину. Эта шина используется для адресации. Каждая ячейка памяти и устройство ввода-вывода компьютера имеет свой собственный адрес.

При считывании или записи данных процессор должен сообщать, по какому адресу он желает прочитать или записать данные, для чего необходимо указать этот адрес.

В отличие от шины данных шина адреса является однонаправленной.

Разрядность адресной шины определяет максимальное число адресов, по которым может обратиться процессор, т. е. число линий в адресной шине показывает, каким объемом памяти может управлять процессор. Учитывая, что одна адресная линия обеспечивает представление одного разряда двоичного числа, формулу для максимального объема адресуемой памяти можно записать в следующем виде:

максимальное число адресов = 2n,

где n — разрядность адресной шины.

Процессор 8088 имел 20 адресных линий, что в соответствии с приведенной формулой обеспечивало адресацию памяти объемом:

220 =1 048 576 байт = 1024 Кбайт = 1 Мбайт.

Это тот самый предельный объем памяти, который все еще имеет силу в операционной системе DOS.

Совсем иная ситуация с процессором 80286. Он имеет 24 адресных линии и поэтому в состоянии управлять памятью объемом:

224= 16 777 216 байт =16 Мбайт.

Для обеспечения связи с микросхемами памяти число адресных линий процессора должно равняться числу адресных линий на системной плате.

Процессоры 80386, 80486 и Pentium имеют 32 адресных линии, что обеспечивает адресацию свыше 4 млрд. ячеек памяти. На системной плате с такими процессорами должно быть 32 линии, обеспечивающие обмен адресами между центральным процессором и всеми важными периферийными микросхемами.

Линии шины управления на системной плате служат для управления различными компонентами ПК. По выполняемой ими функции их можно сравнить с переводной стрелкой на железнодорожных путях.

С помощью небольшого числа линий шина управления обеспечивает такое функционирование системы, чтобы в каждый данный момент времени только одна структурная единица ПК пересылала данные по шине данных или осуществляла адресацию памяти.

К шине может быть подключено много приемных устройств. Сочетание управляющих и адресных сигналов определяет, для кого именно предназначаются данные на шине. Управляющая логика возбуждает специальные стробирующие сигналы, чтобы указать получателю, когда ему следует принимать данные.

Управляющая логика активизирует в каждый конкретный момент только одно устройство, которое становиться ведущим. Когда устройство активизировано, оно помещает свои данные на шину. Все другие микросхемы в этот промежуток времени должны блокироваться с помощью соответствующего сигнала на линии управления.

Микропроцессор взаимодействует с внешней средой с помощью шины адреса/данных/состояния и нескольких управляющих сигналов. Собственно взаимодействие заключается в выполнении одной из двух операций: МП либо выводит (записывает) данные, либо вводит (считывает) данные или команды. В каждой из этих операций процессор должен указывать то устройство, с которым он будет взаимодействовать; другими словами, процессор должен адресовать ячейку памяти либо порт ввода или вывода.

Для передачи данных или выборки команды процессор инициирует так называемый цикл шины. Кроме процессора, цикл шины могут инициировать и другие устройства, например, арифметический сопроцессор.

Цикл шины представляет собой последовательность событий, в течение которой процессор выдает адрес ячейки памяти или периферийного устройства, а затем формирует сигнал записи или считывания, а также выдает данные в операции записи. Выбранное устройство воспринимает данные с шины в цикле записи или помещает данные на шину в цикле считывания. По окончании цикла шины устройство фиксирует записываемые данные или снимает считываемые данные.

Рассмотрим цикл шины микропроцессора 8086, который имеет совмещенную 20-разрядную шину адреса/данных/состояния и шину управления (рис. 4).

Рис. 4. Шины микропроцессора 8086

Цикл шины микропроцессора 8086 состоит минимум из четырех тактов синхронизации, называемых также состояниями T, которые идентифицируются спадающим фронтом сигнала синхронизации CLC. В первом такте (T1) процессор выдает на шину адреса/данных/состояния AD20-AD0 адрес устройства, которое будет источником или получателем информации в текущем цикле шины. Во втором такте (T2) процессор снимает адрес с шины и либо переводит тристабильные буферы линий AD15-AD0 в высокоимпедансное состояние, подготавливая их к выводу информации в цикле считывания, либо выдает на них данные в цикле записи.

Управляющие сигналы, инициирующие считывание, запись или подтверждение прерываний, всегда выдаются в такте T2. В максимальной конфигурации системы сигнал записи формируется в такте T3, чтобы гарантировать стабилизацию сигналов данных до начала действия этого сигнала.

В такте T2 старшие четыре линии адреса/состояния переключаются с режима выдачи адреса на режим выдачи состояния. Сигналы состояния предназначены в основном для диагностических целей, например, идентифицируют сегментный регистр, который участвует в формировании адреса памяти.

В течение такта T3 процессор сохраняет информацию на линиях состояния. На шине данных в цикле записи сохраняются выводимые данные, а в цикле считывания производится опрос вводимых данных.

Тактом T4 заканчивается цикл шины. В этом такте снимаются все управляющие сигналы и выбранное устройство отключается от шины.

Таким образом, цикл шины для памяти или периферийного устройства представляет собой асинхронное действие. Устройство может управлять циклом шины только путем введения состояний ожидания.

Процессор выполняет цикл шины в том случае, когда ему необходимо осуществить запись или считывание информации. Если циклы шины не требуются, шинный интерфейс реализует холостые состояния Ti, в течение которых процессор сохраняет на линиях состояния сигналы состояния от предыдущего цикла шины.

Статьи к прочтению:

Как выбрать видеокарту. Или почему шина 256 бит — не рулит. (см. описание)

Похожие статьи:

Современные устройства радиоэлектронной техники используют большое число микросхем, что требует много линий для адресации, выбора и управления их…

Шины микропроцессорной системы и циклы обмена Самое главное, что должен знать разработчик микропроцессорных систем — это принципы организации обмена…

Источник: csaa.ru

Шина адреса, раздельные и объединенные адресные пространства памяти и устройств ввода-вывода

Шина адреса – шина МПС, используемая микропроцессором или устройствами, способными формировать адрес, для указания физического адреса слова ОЗУ (или начала блока слов) либо внешнего устройства, к которому активное устройство желает обратиться для проведения операции чтения или записи.

Шина адреса АВ (Address Bus), в принципе, может быть однонаправленной. Она предназначена для передачи адреса ячейки памяти или устройства ввода/вывода. Направление передачи по шине адреса — от МП к внешним устройствам. Варианты условных обозначений однонаправленной параллельной шины показаны на рис. 1.3, где стрелка указывает направление передачи.

Рис.1.3. Варианты условных обозначений однонаправленной параллельной 16-разрядной шины

Число 16 на рис. 1.3 обозначает разрядность шины. Допускается обозначение шин и без указания разрядности.

Основной характеристикой шины адреса является её разрядность (ширина) в битах. Ширина шины адреса определяет объём адресуемой памяти. Например, если ширина адресной шины составляет 16 бит, и размер слова памяти равен одному байту (минимальный адресуемый объём данных), то объём памяти, который можно адресовать, составляет 2 16 = 65536 байтов (64 Кбайт). Количество адресуемых ячеек памяти можно рассчитать по формуле:

где I — разрядность шины адреса.

Если рассматривать структурную схему микропроцессора, то адресная шина активизирует работу всех внешних устройств по команде, которая поступает с микропроцессора.

Если шина адреса является однонаправленной, то источником адреса является только одно устройство (например, МП), но тогда один из режимов работы МПС может оказаться невозможным – прямой доступ к памяти (захват магистрали, DMA).

Шина данных

Шина данных служит для пересылки данных между ЦП и памятью или ЦП и устройствами ввода/вывода. Эти данные могут представлять собой как команды ЦП, так и информацию, которую ЦП посылает в порты ввода/вывода или принимает оттуда. Таким образом, данные по шине данных могут передаваться от одного устройства к другому в любом направлении.

Шина данных DB (Data Bus) принципиально является двунаправленной. Она предназначена для передачи данных между блоками МПС. Информация по одним и тем же линиям DB может передаваться в двух направлениях — как к МП, так и от него. Варианты условных обозначений двунаправленной шины показаны на рис. 1.4.

Рис.1.4. Варианты условных обозначений двунаправленной параллельной 8-разрядной шины

Разрядность шины данных определяется разрядностью процессора, то есть количеством двоичных разрядов, которые могут обрабатываться или передаваться процессором одновременно. Разрядность процессоров постоянно увеличивается по мере развития компьютерной техники.

В МП 8088 шина данных имеет разрядность (ширину) 8 бит. В МП 8086, 80186, 80286 ширина шины данных 16 разрядов; в МП 80386, 80486, Pentium и Pentium Pro — 32 разряда.

Подчеркнем, что ШД всегда принципиально двунаправлена (иначе либо чтение, либо запись будут запрещены).

Двунаправленность сводится к тому, что на одну и ту же линию шины в разные моменты времени должны иметь возможность выдавать данные несколько устройств (модулей).

Для того, чтобы модули не мешали друг другу при работе на общую шину, существует 2 варианта исполнения выходных каскадов элементов, работающих на линию системной магистрали:

— элемент с тремя состояниями (с z-состоянием);

— схема с открытым коллектором (рис. 1.5).

Рис.1.5 Выход с открытым коллектором

Шина управления

По шине управления передаются сигналы, определяющие характер обмена информацией по магистрали. Сигналы управления определяют, какую операцию — считывание или запись информации из памяти нужно производить, синхронизируют обмен информацией между устройствами и т.д.

Шина управления СВ (Control Bus) предназначена для передачи управляющих сигналов. Хотя направление управляющих сигналов может быть разным, однако шина управления не является двунаправленной, поскольку для сигналов разного направления используются отдельные линии.

В основу построения подавляющего большинства компьютеров положены следующие общие принципы, сформулированные в 1945 г. американским ученымДжоном фон Нейманом.

1. Принцип программного управления. Программа состоит из набора команд, выполняющихся процессором автоматически в определенной последовательности.

2. Выборка программы из памяти осуществляется с помощью счетчика команд. Этот регистр процессора последовательно увеличивает хранимый в нем адрес очередной команды на длину команды. А так как команды программы расположены в памяти друг за другом, то тем самым организуется выборка цепочки команд из последовательно расположенных ячеек памяти. Если же нужно после выполнения команды перейти не к следующей, а к какой-то другой, используются командыусловного илибезусловного перехода, которые заносят в счетчик команд номер ячейки памяти, содержащей следующую команду. Выборка команд из памяти прекращается после достижения и выполнения команды «стоп». Таким образом,процессор исполняет программу автоматически, без вмешательства человека.

3. Принцип однородности памяти. Программы и данные хранятся в одной и той же памяти, поэтому компьютер не различает, что хранится в данной ячейке памяти – число, текст или команда. Над командами можно выполнять такие же действия, как и над данными.

Это открывает целый ряд возможностей. Например,программа в процессе своего выполнения также может подвергаться переработке, что позволяет задавать в самой программе правила получения некоторых ее частей (так в программе организуется выполнение циклов и подпрограмм).

Более того, команды одной программы могут быть получены как результаты исполнения другой программы. На этом принципе основаныметоды трансляции – перевода текста программы с языка программирования высокого уровня на язык конкретной машины.

4. Принцип адресности. Структурно основная память состоит из перенумерованных ячеек. Процессору в произвольный момент времени доступна любая ячейка. Отсюда следует возможность давать имена областям памяти так, чтобы к запомненным в них значениям можно было впоследствии обращаться или менять их в процессе выполнения программ с использованием присвоенных имен.

Компьютеры, построенные на перечисленных принципах, относятся к типуфон-неймановских. Но существуют компьютеры, принципиально отличающиеся от фон-неймановских. Для них, например, может не выполняться принцип программного управления, т. е. они могут работать без счетчика команд, указывающего текущую выполняемую команду программы. Для обращения к какой-либо переменной, хранящейся в памяти, этим компьютерам необязательно давать ей имя. Такие компьютеры называются не фон-неймановскими.

Источник: helpiks.org

Урок №1-2 по теме Архитектура компьютера. Магистраль: шина данных, шина адреса и шина управления. Шины переферийных устройств

Главная > Урок

| Информация о документе | |

| Дата добавления: | |

| Размер: | |

| Доступные форматы для скачивания: |

Урок №1-2 по теме «Архитектура компьютера. Магистраль: шина данных, шина адреса и шина управления. Шины переферийных устройств.

Цели урока:

Образовательные:

изучить принцип работы компьютера.

помочь учащимся усвоить магистрально-модульный принцип построения компьютера, дать основные понятия, необходимые для начала работы на компьютере.

уметь ориентироваться в функциях отдельных узлов компьютера.

знать основные принципы построения компьютера

Воспитательная:

формирование самостоятельности и ответственности при работе с компьютером

Развивающая:

развитие внимания и аналитического мышления

развитие навыков работы с клавиатурой

Оборудование:

компьютер, компьютерная презентация.

Объяснение нового материала

Персональные компьютеры, более чем какой-либо другой вид ЭВМ, способствуют переходу к новым компьютерным информационным технологиям, которым свойственны:

дружественный информационный, программный и технический интерфейс с пользователем;

выполнение информационных процессов в режиме диалога с пользователем;

сквозная информационная поддержка всех процессов на основе интегрированных баз данных;

так называемая «безбумажная технология».

Компьютер — это многофункциональное электронное устройство для накопления, обработки и передачи информации.

Под архитектурой компьютера понимается его логическая организация, структура и ресурсы, т.е. средства вычислительной системы, которые могут быть выделены процессу обработки данных на определенный интервал времени.

В основу построения большинства ЭВМ положены принципы, сформулированные в 1945 г. Джоном фон Нейманом:

1 . Принцип программного управления (программа состоит из набора команд, которые выполняются процессором автоматически друг за другом в определённой последовательности).

2. Принцип однородности памяти (программы и данные хранятся в одной и той же памяти; над командами можно выполнять такие же действия, как и над данными).

3 . Принцип адресности (основная память структурно состоит из нумерованных ячеек).

ЭВМ, построенные на этих принципах, имеют классическую архитектуру (архитектуру фон Неймана).

Архитектура ПК определяет принцип действия, информационные связи и взаимное соединение основных логических узлов компьютера :

Магистрально-модульный принцип.

Основой архитектуры современных компьютеров является магистрально-модульный принцип организации аппаратных компонентов. Здесь все информационные и управляющие потоки между устройствами организуются с помощью шинной технологии.

В системную магистраль (системную шину) микропроцессорной системы входит три основные информационные шины: адреса, данных и управления.

— это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд. Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями.

Обычно шина данных имеет 8, 16, 32 или 64 разряда. Понятно, что за один цикл обмена по 64-разрядной шине может передаваться 8 байт информации, а по 8-разрядной — только один байт. Разрядность шины данных определяет и разрядность всей магистрали. Например, когда говорят о 32-разрядной системной магистрали, подразумевается, что она имеет 32-разрядную шину данных.

— вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2 N , где N — количество разрядов. Например, 16-разрядная шина адреса обеспечивает 65536 адресов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП).

Как в шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий — логическому нулю. При отрицательной логике — наоборот.

— это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

Сигналы шины управления могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще). Линии шины управления могут быть как однонаправленными, так и двунаправленными. Типы выходных каскадов могут быть самыми разными: с двумя состояниями (для однонаправленных линий), с тремя состояниями (для двунаправленных линий), с открытым коллектором (для двунаправленных и мультиплексированных линий).

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (Рис. 1). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.

Мультиплексирование шин адреса и данных.

Порты и контроллеры.

Рассматривая IBM-совместимую компьютерную архитектуру можно разделить все устройства на системные (процессор, оперативная память и т.д.) и внешние, которые подразделяются на запоминающие (жесткий диск, CR-ROM и т.д.) и устройства ввода/вывода (клавиатура, принтер и т.д.). Каждое из устройств должно подсоединяться к системной шине. Существуют следующие основные способы подключения устройств к системной шине:

— Используется для системных устройств. Обычно встроен в материнскую плату. Устройство подключенное к разъему с точки зрения архитектуры является жизненно необходимым для работы ПК. Системная шина также имеет разъемы на материнской плате для подключения контроллеров. Наиболее распространненными являются PCI, AGP и PCI-Express. Используя разъем устройство подключается непосредственно к системной шине

— Представляет собой аналог разъема с тем отличием, что порт предназначен для подключения внешних устройств не соединяющихся напрямую с материнской платой. Работу устройств подключенных посредством порта обычно контролирует операционнная система. Различают:

параллельные порты, в которых данные передаются параллельными блоками. Последовательные порты: COM.

последовательные порты, в которых данные передаются последовательно друг за другом. Параллельные порты: LPT.

последовательно-параллельные порты, в которых данные передаются последовательно, но параллельными блоками. Последовательно-параллельные порты: USB.

Синонимом порта является интерфейс.

— обеспечивает сопряжение внешнего устройства и системной платы. Контроллеры бывают либо интегрированными (встроенными) в материнскую плату(контроллер клавиатуры, жесткого диска и т.д.), либо выполняются в виде отдельной платы, вставляющейся в разъем на МП, в этом случае контроллер называют адаптером (видеоадаптер, сетевой адаптер и т.д.).

Закрепление изученного материала

Рис. 2 Общая организация узлов и устройств ЭВМ

Источник: gigabaza.ru

Шина управления

Шина данных,

Шина адресная,

ШИНЫ

Шины данных и шины адресов (на физическом уровне) – многопроводные линии с гнездами для подключения электронных схем.

Совокупность проводов магистрали разделяется на отдельные группы: шину адреса, шины данных и шину управления:

Шина адреса предназначена для передачи адреса того устройства (или той ячейки памяти), к которому обращается процессор.

По шине данных передаётся вся информация при записи и считывании.

По шине управления передается управляющий сигнал и сигналы синхронизации.

Процесс взаимодействия процессора и памяти сводится к двум операциям – записи и считывания информации. При записи процессор по специальным проводникам (шина адреса) передает биты, кодирующие адрес, по другим проводникам – управляющий сигнал «запись», и еще по другой группе проводников (шины данных) передает записываемую информацию.

При чтении по шине адреса передается соответствующий адрес оперативной памяти (ОП), а с шины данных считывается нужная информация.

По шине адресов передается также адрес порта ввода — вывода, который нужен для

использования ЦП. Сигнал ввода-вывода определяет направление передачи.

Шины могут соединять ЦП как с памятью, так и с УВВ.

Современные компьютеры имеют прямую связь межу памятью и УВВ, что позволяет осуществлять передачу данных к периферийным устройствам и обратно без участия ЦП.

Этот метод передачи данных называется прямым доступом к памяти (ПДП).

Преимуществом ПДП является то, что скорость передачи обеспечивается только временем доступа к памяти (обычно менее 1 мкс).

Для передачи данных через ЦП требуется несколько команд, и на это уходит в 10-20 раз больше времени.

Прямой доступ к памяти применяется с быстродействующими периферийными устройствами, такими как магнитные диски, быстродействующие линии связи или дисплеи.

1.4 ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР

1.4 ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР

это основной рабочий компонент компьютера, который:

— выполняет арифметические и логические вычисления;

— управляет вычислительным процессом;

— координирует работу всех устройств компьютера.

ЦП обрабатывает данные. Он выбирает команды из памяти, дешифрирует их и выполняет.

ЦП вырабатывает временные сигналы и сигналы управления, передает в память и из памяти и устройств ввода-вывода, выполняет арифметические и логические операции и идентифицирует внешние сигналы.

На рис.1.1.4. показан структура типичного ЦП.

В течение каждого цикла командыЦП выполняет много управляющих функций:

1. помещает адрес команды в адресную шину памяти;

2. получает команду из шины ввода данных и дешифрирует ее;

3. выбирает адреса и данные, содержащиеся в команде; адреса и данные могут находиться в памяти или в регистрах;

4. выполняет операцию, определенную в коде команды. Операцией может быть арифметическая или логическая функция, передача данных или функция управления;

5. следит за управляющими сигналами, такими как прерывание, и реагирует соответствующим образом;

6. генерирует сигналы состояния, управления и времени, которые необходимы для нормальной работы УВВ и памяти.

Таким образом, ЦП является “мозгом”, определяющим действия компьютера.

Не нашли то, что искали? Воспользуйтесь поиском:

Лучшие изречения: Как то на паре, один преподаватель сказал, когда лекция заканчивалась — это был конец пары: «Что-то тут концом пахнет». 8845 —  | 8367 —

| 8367 —  или читать все.

или читать все.

Источник: studopedia.ru

Выполнение транзакций на шине PCI. Реализация на VHDL

Не так давно я спрашивал о механизме опроса PCI-устройств. После я устроился на работу, доделал тестовое задание, а спрашивал я именно о нем, и благополучно забыл о нем. Но недавно выдали новый проект и пришлось все вспомнить, заодно и решил написать сюда.

Транзакций на шине PCI достаточно много, в данном топике будет описаны только следующие:

- Конфигурационные транзакции

- Транзакции ввода/вывода

- Транзакции обращения к памяти

При осуществлении транзакций возможно 2 варианта:

- Когда ведущим устройством является южный мост

- Когда ведущим устройством является устройство, подключенное к шине PCI

Как уже сложилось, при рассмотрении шины PCI, ведущее устройство я буду называть мастером(Master), ведомое — таргетом (Target).

В данной статье рассматриваются только транзакции, когда мастером является южный мост, так как транзакции, когда мастером является устройство, подключенное к шине PCI заслуживает отдельной статьи.

И так, для работы с шиной, нам понадобятся следующие сигналы:

clk (Clock) — обеспечивает синхронизацию всех транзакций на PCI, а также является входным для каждого PCI — устройства.

AD (Address and Data) — мультиплексирования шина адреса и данных.

IDSEL (Initialization Device Select) — выбор устройства инициализации, используется для выбора кристалла при транзакциях чтения конфигурации и записи.

CBE (Bus Command and Byte Enables) — команды шины и разрешение байта.

FRAME (Frame) — сигнал выдаётся мастером в начале транзакции и определяет её длительность. Для однофазных транзакций FRAME всегда длится один такт. При многофазных транзакциях FRAME снимается за один такт до завершения транзакции.

IRDY (Initiator Ready) — сигнал готовности мастера. Он свидетельствует о готовности мастера завершить текущую фазу данных.

TRDY (Target Ready) — сигнал готовности таргета, свидетельствующий о готовности таргета завершить текущую фазу данных.

STOP (Stop) — этот сигнал выдаётся таргетом, если он хочет остановить текущую транзакцию.

PAR (Parity) — контроль четности по линиям AD и CBE.

RST(Reset) — cигнал сброса. Является асинхронным.

DEVSEL (Device Select) — сигнал выбора устройства.

Перед началом работы с любым устройством его нужно инициализировать. Поэтому рассмотрим особенности выполнения конфигурационных транзакций.

Конфигурационные транзакции. Общие сведения.

Для генерации конфигурационных транзакций PCI на ПК используются обращения к двум портам ввода-вывода, носящим имена CONFIG_ADDRESS и CONFIG_DATA, имеющим адреса 0CF8h и 0CFCh соответственно и входящим в состав моста Host–PCI, через который шина PCI прямо или косвенно соединяется с процессором.

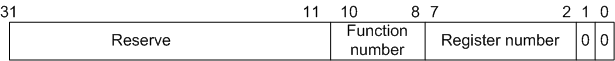

Порт CONFIG_ADDRESS имеет размер двойное слово и доступен только как единое целое. Обращения меньшего размера по принадлежащим ему адресам передаются на шину PCI как обычные транзакции ввода-вывода. Этот порт доступен для чтения и записи и имеет следующий формат:

Когда необходимо выполнить конфигурационную транзакцию, в этот порт записывается адрес регистра конфигурационного пространства PCI, состоящий из номеров шины (разряды 23–16), устройства (15–11), функции (10–8) и собственно регистра (7–2). Биты 1 и 0 должны всегда содержать нули, а старший бит должен содержать единицу, разрешая тем самым выполнение конфигурационной транзакции. Разряды 30–24 зарезервированы и должны содержать нули.

Собственно генерация конфигурационной транзакции происходит при чтении или записи порта CONFIG_DATA, когда в CONFIG_ADDRESS был записан адрес с установленным старшим битом и номером шины, соответствующим шине, подключенной к мосту Host–PCI, или любой шине PCI, лежащей ниже этой шины и соединённой с ней через один или несколько мостов PCI–PCI (допустимый диапазон номеров шин задаётся мосту Host–PCI в процессе его настройки). Доступ к порту CONFIG_DATA должен иметь размер, равный размеру считываемого или записываемого конфигурационного регистра, адрес которого находится в CONFIG_ADDRESS.

Если номер шины, заданный в CONFIG_ADDRESS, совпадает с номером шины, подключённой непосредственно к мосту Host–PCI, генерируется конфигурационная транзакция с адресом типа 0, причём номер устройства, находящийхся в разрядах 15–11 порта CONFIG_ADDRESS, используется для выдачи одного из сигналов IDSEL, которые и служат для выбора конкретного устройства. Кроме того, декодированный номер устройства (один единичный и остальные нулевые биты) в фазе адреса конфигурационной транзакции передаётся в разрядах 31–11 адреса.

Если адрес в CONFIG_ADDRESS указывает не ту шину, которая непосредственно подключена к мосту Host–PCI, последний генерирует конфигурационную транзакцию с адресом типа 1. Она будет обработана мостом PCI–PCI, который опознает содержащийся в адресе номер шины. Этот мост либо выполнит конфигурационную транзакцию с адресом типа 0 (если адресуемое устройство подключено к шине, прямо подсоединённой к этому мосту), либо сгенерирует транзакцию с адресом типа 1, обеспечив тем самым её прохождение через следующий мост. Длина этой цепочки теоретически ограничена только разрядностью поля, отведённого под номер шины (8 бит).

Если при выполнении транзакции выяснится, что адресуемого конфигурационного регистра не существует (указан номер несуществующей шины, устройства, функции или регистра), то операция записи не возымеет никаких действий, а операция чтения вернёт процессору значение, содержащее единицы в каждом разряде

Формат адреса для транзакции типа 1.

Формат адреса для транзакции типа 0.

Формат регистра конфигурации:

Минимальный набор регистров:

- Vendor ID — поле идентифицирует изготовителя устройства. Запрещено использовать значение 0xFFFF.

- Device ID — поле идентифицирует конкретный вид устройства. Запрещено использовать значение 0xFFFF.

- Revision ID — дополнение к идентификатору устройства. Может быть равно нулю.

- Header Type — Для многофункциональных устройств. Если 7ой бит равен 0, то устройство является однофункциональным, иначе — многофункциональное.

- Class Code — доступен только для чтения. Используется для идентификации общего функционального назначения устройства. Старший байт (адрес 0Bh) определяет базовый класс, средний — подкласс, младший — программный интерфейс (если он стандартизован).

- Subsystem ID, Subsystem Vendor ID — задаются производителем. Только для чтения. Хранят идентификаторы, позволяющие точно идентифицировать карты и устройства (в системе могут быть установлены

несколько карт с совпадающими идентификаторами устройства и производителя (Device ID и Vendor ID). - BAR0 — BAR5 — описывают области памяти и портов ввода-вывода.

Для областей памяти и портов описания различаются:

- Бит 0 = 0 — признак памяти. Размером не более 2 Гбайт

- Бит 0 = 1 — признак области портов. Размером до 256 байт.

Размер областей вычисляется следующим образом. В BAR записывается 0xFFFFFFFF. Далее, из BAR считывается значение, и вычитается из 0xFFFFFFFF. Результат и есть размер области. Единица в младшем бите не учитывается.

Общий алгоритм выполнения транзакций

Мастер выставляет на шине AD адрес устройства, на шине CBE выполняемую команду, устанавливает сигнал FRAME в 0 и сигнал IRDY в 0. Далее, мастер ждет от таргета — выставления им сигналов TRDY и DEVSEL. Так же, таргет выставляет на шину AD запрашиваемые данные. Данные считаются валидными, когда IRDY, TRDY и DEVSEL равны уровню логического нуля.

Реализация

Для обращения к выводам ПЛИС потребуются специальные компоненты: буферы ввода/вывода для работы с Z — состоянием.

Так, для шины AD подключение будет выглядеть следующим образом:

Где,

- O — выход буфера.

- IO — вход/выход буфера, непосредственно подключается к выводу ПЛИС.

- I — выход буфера.

- T — управление входом, уровень единицы — вход, уровень нуля — выход.

Для остальных сигналов аналогично, не буду приводить, что бы не загромождать статью.

Как я уже писал выше, при начале транзакции, когда на шине AD выставлен адрес, всегда сигнал FRAME равен нулю. Ниже приведен код, который формирует сигнал AdrPhASE, во время действия которого нужно защелкнуть шину адреса и шину команд для последующей работы. Фактически сигнал AdrPhASE есть ни что иное, как выделение спадающего фронта сигнала FRAME, что однозначно идентифицирует начало транзакции.

Далее, работу всего устройства можно описать с помощью автомата.

Для понимания выше написанного, приведу возможные команды, передаваемые по шине CBE.

- 0010 I/O Read

- 0011 I/O Write

- 0110 Memory Read

- 0111 Memory Write

- 1010 Configuration Read

- 1011 Configuration Write

Каждой команде соответствует свое состояние автомата. Переход в него зависит от текущего состояния шины CBE и шины AD для транзакций обращения к памяти и портам ввода-вывода. Выход в начальное состояние осуществляется по приходу сигнала IRDY от мастера.

Чтение конфигурации

Так выглядит чтение конфигурации в симуляторе:

Запись конфигурации

Запись в порт

На шине AD мастером выставляется номер регистра для записи, в следующем такте выставляются данные, которые нужно записать.

Приведем пример только для записи одного регистра, остальные записываются аналогично.

Чтение порта

Так выглядит запись и чтение порта ввода-вывода:

Запись и чтение памяти

Так выглядит запись и чтение памяти в симуляторе:

Данные на шину AD выводятся следующим образом. В зависимости от состояния автомата, к выходному буферу подключается соответствующий регистр.

Сигнал разрешения выдачи данных на шину AD формируется следующим образом:

Отдельно хотелось бы добавить про компонент STS на примере выработки сигнала DEVSEL

Так как, активные уровни управляющих сигналов равны нулю, то для перехода в Z — состояние и отпускания линии нужно предварительно выдать уровень логической единицы и только потом перевести в Z — состояние.

Заключение

В заключение хочу сказать, что выполнение транзакций на шине PCI не так сложно как кажется. Разработанная прошивка была залита в ПЛИС. Плата с ПЛИС вставлена в PCI слот и был включен компьютер. Система нашла плату и запросила драйвера на нее.

Источник: habr.com